# Keysight U4305B Protocol Exerciser for PCI Express® 3.0

Data Sheet

A multi-personality test instrument for PCIe:

- PCIe root complex and card emulation

- L1 substate emulation

- LTSSM analysis

- PTC PCI-sig compliance test

- NVMe conformance

- RAS system verification

- Multi-root virtualization

### One card: Multiple PCIe Test Applications

### PCIe exerciser U4305B-EX3

Emulate PCIe device or root complex with tools to test and verify operation of equalization, power management, error recover, or complete NVMe emulation, or use the exerciser to replay traffic captured by the U4301B PCIe analyzer.

### Protocol Test Card (PTC) U4305B-021

Test to the protocol standard of the PCI-SIG with our automated test package. Provides independent testing of PCIe add-in cards and BIOS systems with both PCIe 2.0 and 3.0 tests built in.

### LTSSM U4305B-LT3

Perform link negotiations testing and thoroughly test a DUT's LTSSM functions. Verify all the transitions and validate state timeouts. Predefined LTSSM tests assess the LTSSM operation.

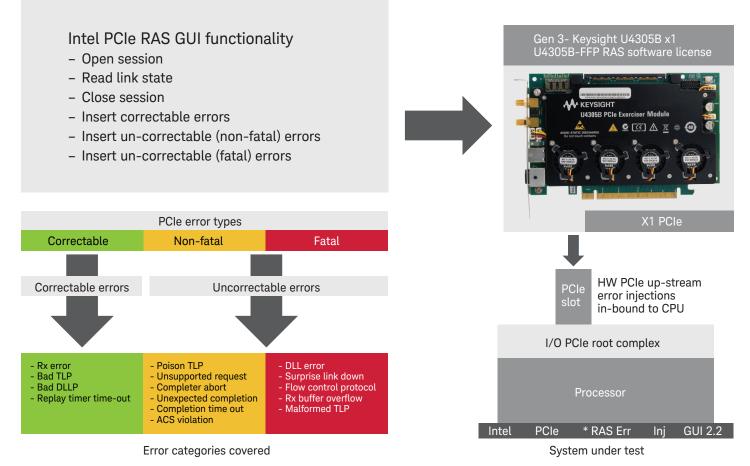

### RAS system validation U4305B-FFP

Intel® RAS validation framework now utilizes the Keysight U4305B PCIe 3.0 exerciser card to enable fault and error injection for testing of RAS features, allowing you to ensure the system performance, resiliency and reliability when faults occur.

| Feature                                                          | PCIe exerciser<br>U4305B-EX3 | PTC – Protocol Test Card<br>U4305B-021 | LTSSM tests<br>U4305B-LT3 | RAS system validation<br>U4305B-FFP |

|------------------------------------------------------------------|------------------------------|----------------------------------------|---------------------------|-------------------------------------|

| General settings                                                 |                              |                                        |                           |                                     |

| – Session type: to upstream (EP)                                 | $\checkmark$                 |                                        | $\checkmark$              |                                     |

| <ul> <li>Session type: to downstream (RC)</li> </ul>             |                              |                                        |                           |                                     |

| – Link settings<br>– Equalization settings                       | $\checkmark$                 | √ x1 link only                         |                           |                                     |

| <ul> <li>Transceiver settings</li> <li>Lane settings"</li> </ul> |                              |                                        |                           |                                     |

| – Skip settings<br>– Pattern matcher                             | $\checkmark$                 |                                        |                           | API only                            |

| – Trigger out                                                    |                              |                                        |                           |                                     |

| <ul> <li>Algorithmic payload</li> </ul>                          |                              |                                        |                           |                                     |

| <ul> <li>Power management (LOs, L1, L1 substate)</li> </ul>      |                              |                                        |                           |                                     |

| PCI-SIG compliance tests (PTC)                                   |                              | \                                      |                           |                                     |

| LTSSM tester                                                     |                              |                                        |                           |                                     |

| Traffic setup                                                    |                              |                                        |                           |                                     |

| <ul> <li>Three functions</li> </ul>                              | $\checkmark$                 |                                        |                           | API only                            |

| <ul> <li>Additional functions</li> </ul>                         | Optional                     |                                        |                           |                                     |

| Decoder (BAR values)                                             | $\checkmark$                 |                                        |                           | API only                            |

| Config space                                                     | $\checkmark$                 |                                        |                           | API only                            |

| Data memory                                                      | $\checkmark$                 |                                        |                           | API only                            |

| Virtual channel                                                  | $\checkmark$                 |                                        |                           | API only                            |

| SR-IOV                                                           | Optional                     |                                        |                           |                                     |

| MR-IOV                                                           | Optional                     |                                        |                           |                                     |

| ECRC                                                             | Optional                     |                                        |                           | Optional                            |

| Error insertion                                                  | $\checkmark$                 |                                        |                           | API only                            |

| Protocol checker                                                 | $\checkmark$                 |                                        |                           |                                     |

| DUT config space explorer                                        | $\checkmark$                 |                                        |                           |                                     |

| NVM express                                                      | Optional                     |                                        |                           |                                     |

| Test bench                                                       |                              |                                        |                           |                                     |

| <ul> <li>PCIe only</li> </ul>                                    |                              |                                        |                           |                                     |

| <ul> <li>NVMe conformance</li> </ul>                             | Optional                     |                                        |                           |                                     |

| API access (restricted as per license)                           |                              |                                        |                           |                                     |

| API command logger                                               |                              |                                        |                           |                                     |

### Overview

- Supports Gen1 (2.5 GT/s), Gen2 (5.0 GT/s), and Gen3 (8.0 GT/s) speeds

- x1, x2, x4, x8, or x16 link widths

- Standard height, half-length card

- Perform thorough PCIe® Link testing

- Power management testing of LOs, L1, and L1 substates.

The Keysight U4305B Exerciser can be configured to provide sub-protocol layer test and debug for legacy and next generation PCIe devices. The U4305B Exerciser for PCIe is an advanced traffic generator that can be used to send and respond to TLP, DLLP, and physical layer packets to stimulate PCIe devices and systems. The Exerciser operates in one of three modes, PCIe, MR-IOV, or SR-IOV. The capabilities of these modes can be enhanced with the purchase of additional software licenses. Specific DUT test case requirements can be written by means of the included API. U4305B is a standard height, half-length PC form factor card as described in the PCI Express specification, and fits into every system including blade servers.

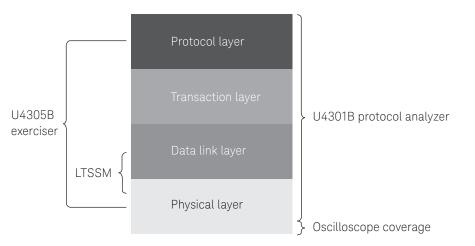

The PCI Express test and debug capabilities of the U4305B is broken down into the sub-protocol layers of the specification as shown in Figure 3. By emulating a PCIe component (with or without MRIOV capabilities), the Keysight U4305B Exerciser acts as an ideal link partner by sending appropriate I/O traffic to stimulate the device under test. The device under test can be exercised under various conditions and scenarios without influencing the performance parameters of the device under test. The Keysight U4305B Exerciser can send a block of TLP requests of 32- or 64-bit memory, I/O, Configuration, or Message types as stimulus to the device under test. It can also be used to send completion packets in response to DUT's requests.

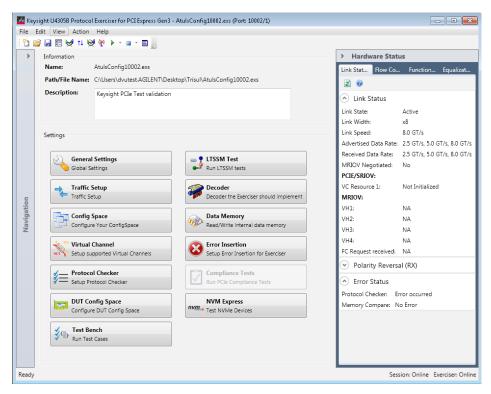

Figure 1. The U4305B can emulate host or add-in card and tests all Gen3 link speeds and widths. Simple controls for traffic generation and error detection or insertion are simple to access and configure.

## U4305B-EX3 PCIe Gen3 Exerciser

The U4305B PCIe 3.0 exerciser provides the following:

- Standard features

- Emulate root complex or add-in-card

- Equalization and transceiver control

- Configuration space register emulation

- Emulates three device functions

- Traffic generation

- Data replay of data captured on U4301A/B PCIe analyzer

- Error simulation (CRC errors, bit errors, poison TLP, etc.)

- Protocol exerciser GUI provides a graphical control of the U4305B exerciser card

- API program control can be done through TCL, Python, C++, or C#

- Optional features

- Support up to five functions

- ECRC support

- Provides emulation of MR-IOV capable component

- Provides emulation of SR-IOV capable components

- NVMe emulation of root complex (includes conformance tests)

- NVMe emulation of end point

The built-in "Test Bench" allows user generation on automated testing of PCIe or NVMe operations. The Test Bench comes with scripts that validate the operation from ASPM or PCI-PM L1 substates. These pre-written tests exercise each state 1000 times and provide pass/fail results that report on the control register operation as well as operation of each L1 substate entry/recovery.

Additional testing can be created that utilizes any DCOM-capable language such as TCL, Python, C++, or C# to execute test and generate reports. The exerciser even has API logging that allows the user to create an automated test structure by using the interface.

The built in "Test Bench" allows user generation on automated testing of PCIe or NVMe operations. Users can utilize any DCOM-capable language such as TCL, Python, C++, or C# to execute test and generate reports.

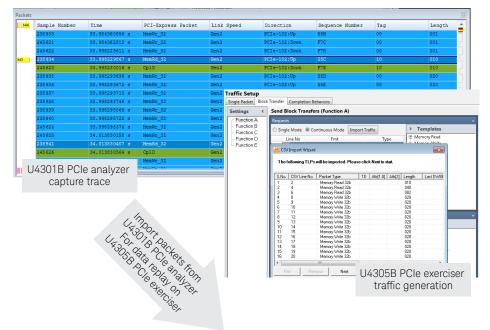

Data captured by the U4301B PCIe analyzer can be replayed by the exerciser to emulate your device. Simple export, edit and replay tools make the process easy.

### Data link layer test features

- Receive a packet as having an LCRC error and NAK in the packet to stimulate DUT response mechanism. Can repeat this for N (N is programmable) for a programmable sequence number causing DUT to replay multiple times and link retraining

- Can offset Sequence number of transmitted packet for sequence number testing of the DUT

- Can send TLPs with LCRC and/or disparity errors

- Programmable replay timer value

### Transaction layer test features

- Can generate 32 bit or 64 bit memory transactions, Configuration Cycles, I/O Cycles, and message requests

- Generate correct or incorrect ECRC and check the same at the receiver

- Generate malformed TLP by making field inconsistent with actual payload length

- Generate poisoned TLP and nullified TLP

- Delay or discard erroneous completion notification to force completion notification

- Supports Data Compare to check integrity of the payload

### Exerciser protocol checker

The U4305B PCIe Gen3 Exerciser provides an internal protocol check that reports various protocol errors that the DUT may have made and has been detected at the Exerciser's receiver. An external trigger can be generated on these events to enable trace tools to capture the details of the error condition.

### U4305B-EX3 PCIe Gen3 Exerciser (Continued)

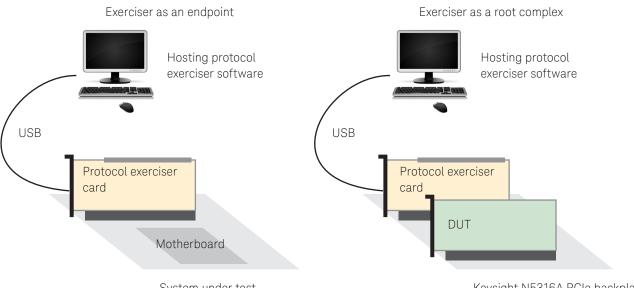

### As an endpoint

When emulating an endpoint, the Keysight U4305B Gen3 exerciser card is plugged into a PCIe slot on the motherboard, as a normal PCIe device. In this scenario, the exerciser card can be used to perform load and stress testing of the system under test.

### As a root complex

When emulating a root complex, the Keysight U4305B Gen3 exerciser card communicates with the device under test through the Keysight N5316A backplane board. In this configuration, the exerciser communicates to the DUT through the bottom connectors. The DUT receives its power from the backplane.

Figure 6 shows example setups of a protocol exerciser card emulating an endpoint and a root complex.

Figure 3. Application coverage of the Keysight U4305B PCIe 3.0 exerciser module.

System under test

Keysight N5316A PCIe backplane

Figure 4. U4305B PCIe exerciser as endpoint and root complex applications.

### Power Management

Power is a critical component of every PCIe system today, and you need it to allow the verification of the LTSSM power saving states. The U4305B enables you to emulate the power management states of LTSSM. With support for both ASPM (Active State Power Management) and PCI-PM (PCI Bus Power Management), the U4305B supports testing to allow you to verify entry and exit to these link states.

| Power Management                                                           |  |  |  |  |

|----------------------------------------------------------------------------|--|--|--|--|

|                                                                            |  |  |  |  |

| Enter L0s after having seen no TLP/DLLP for(ns):                           |  |  |  |  |

| Exit L0s when the following timeout(ns) expires:                           |  |  |  |  |

| On exit send the following number of FTS: 240                              |  |  |  |  |

| ✓ On exit send SKP Ordered Sets                                            |  |  |  |  |

|                                                                            |  |  |  |  |

| TS Settings                                                                |  |  |  |  |

| N_FTS shown in TS at Gen1 speed:                                           |  |  |  |  |

| N_FTS shown in TS at Gen2 speed:                                           |  |  |  |  |

| N_FTS shown in TS at Gen3 speed:                                           |  |  |  |  |

| ,                                                                          |  |  |  |  |

|                                                                            |  |  |  |  |

| Enter ASPM L1 after having seen no TLP/DLLP for (ns):                      |  |  |  |  |

| 🔽 Exit L1 (ASPM or PCI-PM) when following timeout (ns) expires: 30000 🛨    |  |  |  |  |

| Enable aggressive mode for PCI-PM L1                                       |  |  |  |  |

| L1 Substate                                                                |  |  |  |  |

|                                                                            |  |  |  |  |

|                                                                            |  |  |  |  |

| Initiate Entry into L 1.1 or L 1.2 after this much time spent in L 1 (ns): |  |  |  |  |

| 🔽 Enable L1.1                                                              |  |  |  |  |

| 🔽 Enable L1.2                                                              |  |  |  |  |

| ✓ Assert CLKREQ# in all non-L1 states                                      |  |  |  |  |

| Assert CLKREQ# in L1 state                                                 |  |  |  |  |

| Time from CLKREQ# deassertion to Transmitter Power OFF (TPower_OFF) (ns):  |  |  |  |  |

| Time from CLKREQ# assertion to Transmitter Power ON (TPower_ON) (ns):      |  |  |  |  |

Figure 5. LOs enter and recovery is the first step to reducing power consumption when recovery time is critical. Additional power saving are available by using the L1 and L1 substates, but verification of recovery is key. Other testing (NVMe emulation, data replay, traffic and error generation) can be implemented while the power management settings continue to operate on the link as specified. Use scripting to link together multiple operations to recreate your desired test scenario.

| Test Bench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Setup Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                 |

| Test Selection 🕂                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Settings                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PCIe Settings<br>Initialization Script<br>Start  © Use auto © Use custom<br>Script File: CAProgram Files (x86)\Keysight\SPT\PCIEExerciserGen3\8 |

| Entry and exit from PCI-PM L1.1 Entry and exit from PCI-PM L1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Description Code -                                                                                                                              |

| Entry and exit from PCI-PM L1 (L1.0)     Entry and exit from PCI-PM L1 (L1.0)     User Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Testcase 1: Entry & exit from ASPM L1.1.                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Prerequisites: 1. Verify that Link is UP 2. Verify that Current LTSSM State is L0 or L0s or L1.Idle or L1.1.Idle                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | or L1.2.idle                                                                                                                                    |

| ۰                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C:\Program Files (x86)\Keysight\SPT\PCIEExerciserGen3\8.76 Release\Conformance\PCIE                                                             |

| Log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4                                                                                                                                               |

| 🗈 🜉 🖏                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                 |

| Programming memory read packet.<br>Sending memory read packet and verifyin<br>LTSSM state verified for 0 iterations.<br>LTSSM state verified for 100 iterations<br>LTSSM state verified for 200 iterations<br>LTSSM state verified for 300 iterations<br>LTSSM state verified for 500 iterations<br>LTSSM state verified for 500 iterations<br>LTSSM state verified for 700 iterations<br>LTSSM state verified for 500 iterations |                                                                                                                                                 |

| Test case passed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                 |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                                                                                                                                               |

Figure 6. The scripting test bench includes example verification scripts of L1 substate tests.

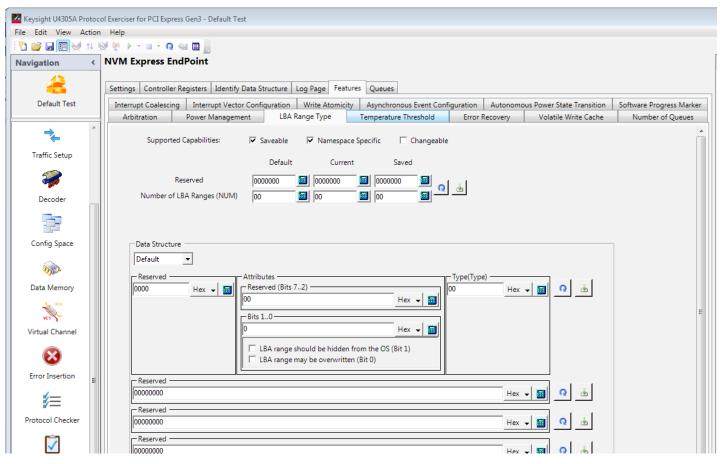

# U4305B-2FP NVMe RC and Endpoint Emulation

Using the U4305B as an NVMe device allows the user to verify the proper operation of the storage devices. The user gains easy access and control of all of the device configuration space registers and all NVMe controller operations for fast and easy scenario testing.

- Exerciser allows the RC device to configure its controller registers as an NVMe endpoint and to start NVMe traffic on the exerciser.

- The supports MSI and MSI-X interrupt mechanisms so the RC device can use these mechanisms. The exerciser can respond to interrupts sent via MSI or MSI-X and fetch commands from the submission queues, execute them and write back completions in the completion queues.

- The exerciser allows you to set up the values in the controller registers and also set values for data structures such as identify structures and log pages. It will also let you set the values for device features to be used with the Get/Set features command.

- The exerciser shows up as two drives in the SUT.

Figure 7. U4305B exerciser can perform all of the functions of an NVMe endpoint with easily modifiable operational parameters.

# U4305B-LT3 LTSSM Testing

### As an LTSSM tester

The Link Training and Status State Machine (LTSSM) is the sub-block that drives and controls the link initialization and training process for a PCIe device to enable the normal data exchange between PCIe nodes on the link. LTSSM operates at the physical layer and exchanges physical layer packets (Ordered sets such as TS1 and TS2) to initialize, train, and manage the link. LTSSM features are provided when option LT3 is purchased.

The Keysight U4305B Exerciser provides positive and negative test cases to exercise critical functions of either the end node (adaptor card) or root complex (motherboard or blade). These test cases can force either DUT target devices into various LTSSM states, verify the state transitions, and timeout implementations, and report the test case results as either Passed or Failed.

### LTSSM physical layer test features

- Supports six way speed change from any of the three speeds to any of the three speeds

- When programmed as an Upstream Component (USC), supports going to Gen3 speed with all phases of equalization (0 through 3), only phase 1, or without equalization

- When programmed as a Downstream Component (DSC), it follows USC in equalization process

- Supports automatic or manual enabling/disabling of the lane reversal feature

- Supports independent lane polarity inversion setting for all the lanes

- Supports physical link widths x1, x2, x4, x8, and x16. Link width is fixed and is specified when ordering

- Supports option to enable/disable scramble modes for Gen1 and Gen2 speeds

- Supports all possible SKIP ordered sets (OS) at transmitter for all three speeds

- Can replace STP/END of a transmitted packet by programmable character at Gen1 and Gen2 speeds. Can corrupt FCRC of STP Token at Gen3 speed

- Supports programmable Transceiver Settings covering a wide range of transmitted signal amplitude and emphasis levels

- Supports programmable Equalization settings sent in Transition Ordered Sets (TS OS) to request the DUT to transmit at various signal amplitude and emphasis levels

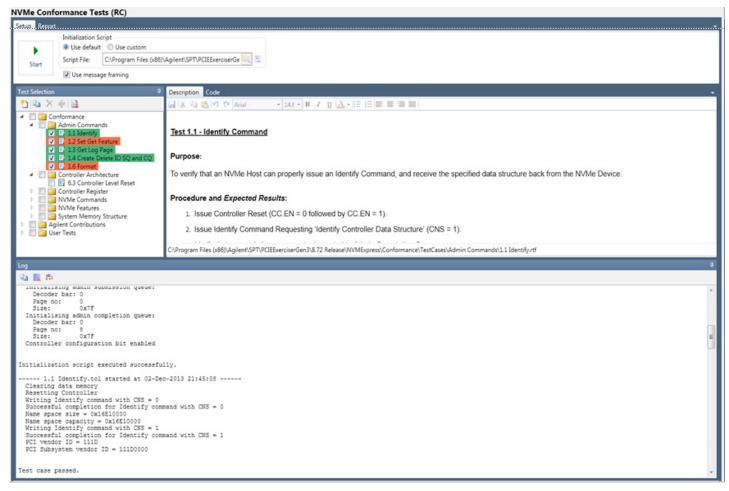

### NVMe Conformance Testing

### Included with U4305B-1FP and U4305B-2FP options

Standardized testing not only improves the adherence to the specification and increases device interoperability, but it also decreases test time by providing tests that give developers insight into device operation. Keysight is proud to implement the NVMe conformance tests as defined by the University of New Hampshire (UNH) Interoperability Lab (IOL). These tests provide pass/fail/warning results with detailed diagnostic information to improve NVMe validation.

The conformance test implements 38 tests for validating NVMe and admin commands, features, and process operations.

Included in the NVMe test package is a complete programming interface to allow the user to extend the automated test procedures. All of the NVMe conformance tests are implemented using the TCL scripting environment, and scripts are open to user modification. The scripting environment includes a TCL language editor with autocomplete features.

Figure 8. The NVMe conformance test suite 1.1 testing is implemented in an easy-to-use validation framework.

### U4305B-EX3 PCIe Gen3 Exerciser Test Automation

The U4305B PCIe exerciser supports a rich programming interface that allows automation of all of the exerciser capabilities. Programming can be done via TCL, which is part of the controller PC software package. Experienced users may directly use the API through its COM interface within other programming languages as well. (Examples are included for TCL, Python, C++, and C#.)

API programs can control the exerciser to do complete PCIe test automation. The program can also share the control with the GUI, allowing the user to automate some tasks and still use the exerciser GUI for manual control.

In order to simplify programing, the U4305B includes an API program logging console. To use this tool, the user simply launches the API console, chooses and preferred programming language, and then uses the exerciser GUI interface to perform a test. Then save the program and add any loops, test conditions, or other program operations of interest.

Note that the following API calls are NOT logged: Calls initiated through PTC, LTSSM, or NVMe conformance test suite.

You can view the API logs in the following formats:

- TCL

- C#

- C++

- Python

- Plain text

| Test Bench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Setup Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Test Selection 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Settings 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Test Selection       4         Image: Selection       5         Image: Selection       5         Image: Selection       6         Image: Selection       6         Image: Selection       7         Image: Selection       7 </td <td>Settings       1         NVMe Settings       Initialization Script         Start       Use auto       Use 32 bit       Use custom         Script File:       C\Program Files (x86)\Keysight\SPT\PCIEExerciserGen3\8.76 Release\V       Image: Compare NVM Command         Description       Code       Image: Compare NVM Command       Image: Compare NVM Command         Purpose:       To verify that a NVMe system can properly execute the Compare NVM Command.       Image: Compare NVM Command         Procedure and Expected Results:       Image: Compare NVM Command       Image: Compare NVM Command</td> | Settings       1         NVMe Settings       Initialization Script         Start       Use auto       Use 32 bit       Use custom         Script File:       C\Program Files (x86)\Keysight\SPT\PCIEExerciserGen3\8.76 Release\V       Image: Compare NVM Command         Description       Code       Image: Compare NVM Command       Image: Compare NVM Command         Purpose:       To verify that a NVMe system can properly execute the Compare NVM Command.       Image: Compare NVM Command         Procedure and Expected Results:       Image: Compare NVM Command       Image: Compare NVM Command |

| Entry and exit from PCI-PM L1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1. Issue Controller Reset (CC.EN = 0 followed by CC.EN = 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Entry and exit from PCI-PM L1 (L1.0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C:\Program Files (x86)\Keysight\SPT\PCIEExerciserGen3\8.76 Release\Conformance\NVMExpress\TestCases\NVM C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | a<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Figure 9. The Test Bench is an easy-to-use automation environment that can generate reports and comes with example TCL automation scripts.

### U4305B-024 Five Function Emulation U4305B-025 MRIOV Emulation U4305B-026 SRIOV Emulation

### Exerciser as a NON-IOV PCIe device

The Exerciser behaves as NON-IOV End Point (EP) or Root Complex (RC) when the protocol is set to PCIe. In this mode the U4305B Exerciser has three hardware channels and each channel is associated with a specific function (F0, F1, and F2). The traffic in each channel can be programmed independently either through the GUI or through the PCI port.

Two additional functions can be obtained with the purchase of the Option 024 software license.

### Exerciser as a SR-IOV capable device

The exerciser behaves as a SR-IOV capable End Point (EP) or Root Complex (RC) when the protocol is set to SR-IOV. In this mode it is compliant with SR-IOV specification Rev. 1.1 (September 8, 2009).

In this configuration the exerciser supports the following:

- One Non-IOV function

- Two Physical Functions (PF)

- Two virtual channels (VCO and VC(x))

- Two virtual functions (VF1 and VF2) per PF

### Multi-root testing

If you want to test an MRIOV-capable PCIe switch, then the protocol exerciser needs to emulate a PCIe device with MRIOV capabilities. The MRIOV license enables the exerciser to emulate an MR- (multi-root) enabled PCIe device. As an MRIOV-capable device, the exerciser supports up to five virtual hierarchies at a time.

The Keysight PCIe protocol exerciser can perform the link negotiation, initialization and training, data link layer functions, and handle incoming requests and completions as per the:

- PCI Express 3.0 base specification for testing a non-IOV PCIe component

- MRIOV specifications revision 1.0 for testing an MRIOV capable PCIe component

- SRIOV specifications revision 1.1 for testing an SRIOV capable PCIe component

| Primary option      | ry option RAS-FFP Exerciser license -EX3 |   |             | Exerciser + Five function (EX3 + 024) |   |             |             |

|---------------------|------------------------------------------|---|-------------|---------------------------------------|---|-------------|-------------|

|                     | RAS-FFP                                  | - | SRIOV (026) | MRIOV (025)                           | - | SRIOV (026) | MRIOV (025) |

| IOV options         | RAS-FFP                                  | - | -026        | -025                                  | - | -026        | -025        |

| Functions           | 3                                        | 3 | 3           | 3                                     | 5 | 5           | 5           |

| Virtual functions   |                                          |   | 4           | 4                                     |   | 8           | 8           |

| Hardware channels   | 3                                        | 3 | 7           | 7                                     | 5 | 13          | 13          |

| Virtual channels    | 2                                        | 2 | 2           | 1                                     | 2 | 2           | 1           |

| Completion queues   | 2                                        | 2 | 2           | 3                                     | 2 | 2           | 5           |

| Virtual link        |                                          |   |             | 1                                     |   |             | 1           |

| Virtual hierarchies |                                          |   |             | 3                                     |   |             | 5           |

The Keysight U4305B can be optioned to support multiple functions, virtual functions, and virtual hierarchies.

# U4305B-FFP PCIe RAS Test Software License

### Description

Intel RAS (reliability, availability and serviceability) validation framework now utilizes the Keysight U4305B PCIe 3.0 exerciser card to enable fault and error injection for testing of RAS features, allowing you to ensure the system performance, resiliency, and reliability when faults occur.

### Solution structure

- Intel PCI express RAS Validation tool kit

- Keysight U4305B PCIe 3.0 exerciser card

- Keysight PCIe RAS test software license 3.0 (or Keysight PCIe 3.0 exerciser software license)

- Intel PCI express hardware error injection GUI software (available from Intel CDI)

- PCI express injection tool overview, order guide, user guide (available from Intel CDI)

Figure 10. Using the RAS test scripts from Intel, testing fault operations provides validation of the RAS error framework.

# U4305B-021 Protocol Test Card 3.0

### Description

Option 021 protocol test card is a Keysight Technologies, Inc. third-generation PCIe 3.0 link and transaction compliance test tool. Designed to the requirements of the PCI-SIG®, the industry organization chartered to develop and manage the PCI Express standard, the PTC3 will provide the Independent Hardware Vendor (IHV) and Independent BIOS Vendor (IBV) with link transaction test results designed to maximize interoperability and conform to current PCIe 3.0 industry protocol specification.

The PCI Express 3.0 link and transaction layer tests require the use of one Protocol Test Card (PTC). The PCI-SIG has approved the use of the Keysight U4305B protocol test card for PCIe 3.0 compliance testing. It is considered a pass if a product passes all tests on this system at a compliance workshop. Please see the PCISIG.com website for more details on these test procedures.

The PCI-SIG has developed test procedures for PCI Express Link Protocol Testing and PCI Express Transaction Protocol Testing to test add-in card compliance to the specification requirements. It also supports the PCI Express Platform BIOS test to exercise the platform BIOS to make sure it properly detects and initializes PCI Express devices.

# Key features and specifications

- PCIe 3.0 link and transaction compliance testing

- PCI-SIG-approved testing for PCIe Gen3

- Includes PCIe 2.0 and PCIe 3.0 protocol test cases

- Supports PCIe 2.5 Gb/s, 5 Gb/s and 8 Gb/s speeds

- Requires only x1 lane width U4305B hardware

- PTC3 software can be used on x4, x8, and x16 lane width U4305B

- Requires N5316A test

- backplane to test add-in cards

| 💕 🖬 🗉 😾 💷        | Help                                                     |                                                                                                                                                           |                                           |

|------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| vigation <       | Compliance Tests                                         |                                                                                                                                                           | > Hardware Status                         |

|                  | •                                                        |                                                                                                                                                           | Link St Flow C Functi Equaliz             |

|                  | Finished                                                 |                                                                                                                                                           |                                           |

| Untitled1        | Report Setup                                             |                                                                                                                                                           |                                           |

|                  | AddInCard Tests                                          | Description                                                                                                                                               | - 💿 Link Status                           |

| ea 📍 🔺           | PTC II                                                   | Test EQUALIZATION_PRESETS (To check that the DUT correctly responds to Link Equali<br>DTC modement the following a strictling                             | Link State: Active                        |

| •- <sup>2</sup>  |                                                          | PTC performs the following activities:<br>1. Set exerciser to use presets.                                                                                | Link Width: x1                            |

| LTSSM Test       |                                                          | 2. Perform Link Up.                                                                                                                                       | Link Speed: 8.0 GT/s                      |

| _                |                                                          | 3. Set Tx preset value.<br>4. Perform equalization.                                                                                                       | Advertised Data Rate: 2.5 GT/s, 5.0 GT/s, |

| <b>~</b>         |                                                          | 5. Skip test in case of link up failure.                                                                                                                  | Received Data Rate: 2.5 GT/s, 5.0 GT/s,   |

| Traffic Setup    |                                                          | 6. Read Tx preset value and reject coefficient in received TS1.<br>Tx preset should be same as the one transmitted. Reject coefficient should be 1 when T | MRIOV Negotiated: No                      |

|                  |                                                          | 7. Repeat for all Tx preset values.                                                                                                                       | PCIE/SRIOV:                               |

|                  |                                                          | Test case ends in a PASS if all above conditions are met<br>∢ [ III                                                                                       | VC Resource 1: Not Initialized            |

| Decoder          | DLL_05_02_17                                             | Quick Test Selection                                                                                                                                      | MRIOV:                                    |

| Decoder          |                                                          |                                                                                                                                                           | VH1: NA                                   |

|                  |                                                          |                                                                                                                                                           | VH2: NA                                   |

| =                |                                                          | CorruptedDLLPs                                                                                                                                            | VH3: NA                                   |

| Config Space     | E. ♥ PTC III                                             | Duplicate I LPSeqNu<br>m                                                                                                                                  | VH4: NA                                   |

|                  | E ASPM_L1                                                | LinkRetrainOnRetryFail                                                                                                                                    | FC Request received: NA                   |

| 2000             |                                                          | LinkKetrainOnRetryFailNoAckNa                                                                                                                             | Polarity Reversal (RX)                    |

| Data Memory      | FLR_CHECK_RESET                                          | rk<br>ReplayNumTest                                                                                                                                       | Lane (07): 0 1 2 3 4 5 6                  |

| L, YO            | L1_FOR_D3_STATE                                          | ReplayTimerTest                                                                                                                                           | State (07): N N N N N N N                 |

|                  |                                                          | Develop TI DOvelop                                                                                                                                        | Lane (8.15): 8 9 10 11 12 13 14 1         |

| Virtual Channel  |                                                          | Y ReservedFieldsDLLPReceive                                                                                                                               | State (815): N N N N N N N                |

|                  | ⊕ · ☑ LTR_ENABLE_CLEARED<br>⊕ · ☑ LTR_NON_D0_STATE       | ReXmitOnNak                                                                                                                                               | Error Status                              |

|                  |                                                          | UndefinedDLLPEncoding                                                                                                                                     | Protocol Checker: Error occurred          |

| Error Insertion  | CONTRACTION_COEFFICIENTS     EQUALIZATION_INITIAL_PRESET | Transaction Layer Link Layer                                                                                                                              | Memory Compare: No Error                  |

|                  | EQUALIZATION_PRESETS                                     |                                                                                                                                                           | -                                         |

| ý <u>—</u>       |                                                          |                                                                                                                                                           |                                           |

| Protocol Checker |                                                          | Add your comment here Evecution                                                                                                                           |                                           |

| TO LOCOT CHECKER |                                                          | Message Framing                                                                                                                                           |                                           |

|                  |                                                          | 🗌 🔲 Subtest PopUp                                                                                                                                         |                                           |

|                  |                                                          | Testing Mode                                                                                                                                              |                                           |

Figure 11. PCIe link and transaction tests as defined by the PCI-SIG provide easy-to-understand pass/fail results.

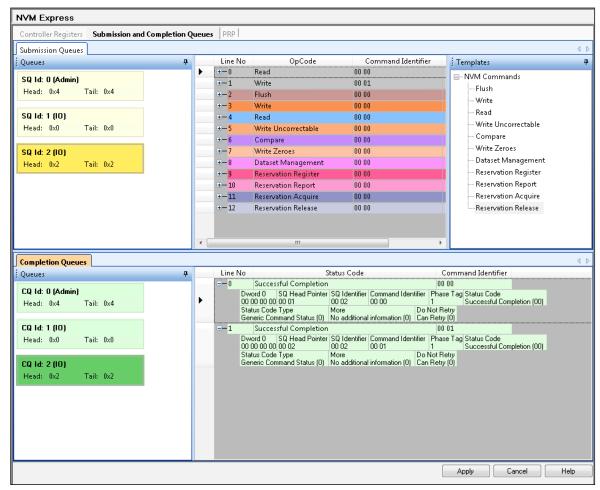

### U4305B-1FP NVMe RC Emulation

### Description

As an NVMe root complex, the exerciser submits various requests (NVMe commands) to an NVMe DUT for completion. These commands include admin commands submitted to the admin queue as well as the I/O commands submitted to the I/O submission queue(s). By sending NVMe command requests to the DUT, you can check how the NVMe controller responds to and completes these requests. You can also verify how the NVMe controller handles admin requests such as queue management or controller initialization. Create multiple submission and completion queues and then use the easy-to-use drag and drop interface to create and send NVMe commands.

- View and configure NVMe controller registers of DUT

- Configure the admin submission and completion queue attributes

- Initialize and configure the interrupt mechanism

- Initialize, view, and edit the MSI- X table of the DUT

- Create up to 64 I/O submission and 64 completion queues

- Add NVMe commands to submission queues and increase the doorbell accordingly. The commands are available as predefined templates

- View the commands and their subsequent completions in the completion queues

- Create PRP lists and PRP entries that can be used in the submitted NVMe commands for data transfer

- Create SGL entries and SGL lists for validating support of Scatter Gather operations

Figure 12. Create up to 64 submission and 64 completion queues, and easily execute queue management commands.

# PC Requirements

A Microsoft Windows PC is used to control the operation of the PCI Express exerciser. You can use the protocol exerciser GUI to control, manage, and use the protocol exerciser card.

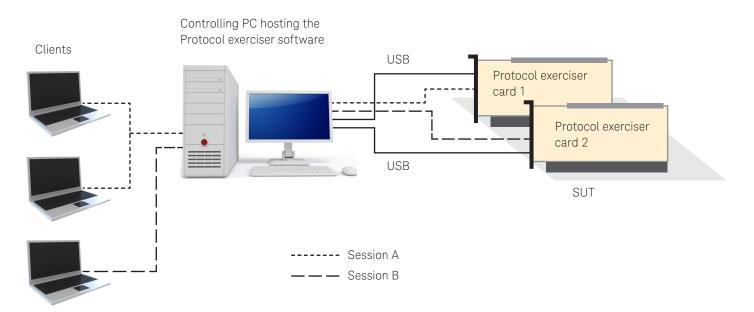

Multiple clients can remotely connect to a single U4305B exerciser session on the controller PC. Figure 3 shows an exerciser session scenario in which Session A and Session B have been created on the controller PC with two U4305B exerciser cards. Two clients are accessing Session A and one client is accessing Session B.

### Controller and client PC requirements

- USB 2.0 interface for each exerciser card

- Pentium processor 1 GHz or equivalent

- Windows XP (with Service Pack 3) or Windows 7 (Enterprise or Professional 32-bit or 64-bit) operating system

- At least 256 MB RAM. For better performance, Keysight recommends the installation of at least 512 MB RAM

- At least 500 MB free disk space on the C drive

Figure 13.

# Specifications and Characteristics

| Size       | Standard height half-length PCIe module 106.7 mm (4.2 inches) high and 167.65 mm (6.6 inches) long                                                                                                                                                                                                                                                         |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Weight     | 408 gr (0.9 lb)                                                                                                                                                                                                                                                                                                                                            |

|            | Shipping weight: 2.36 Kg (5.2 lb)                                                                                                                                                                                                                                                                                                                          |

| Connectors | Power input, USB 2.0B, and two SMA(f) connectors for trigger in and out. Edge connector width is determined by the product configuration purchased. Note: The edge connector is not upgradable after purchase and Keysight does not recommend or support the use of lane adaptors as they have a negative impact on the unit's performance at high speeds. |

| Power requirements     |                                                             |

|------------------------|-------------------------------------------------------------|

| Input                  | 15 Vdc, 10 A maximum                                        |

| Power dissipation      | 70 W maximum                                                |

| Keysight part number 0 | 1950-5159 external power supply supplied with the Exerciser |

| Input                  | 100 to 240 V at 3.5 A maximum, 50 to 60 Hz                  |

#### LTSSM supported states

The Keysight U4305B supports seven of the 11 LTSSM states. The supported states are:

- Detect

- Quiet

- Configuration

- LO

- Recovery

- LOs

- L1

#### U4305B trigger specifications

| e leees alggel opeen | inductions and inductions |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trigger output       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Source impedance     | 50 ohms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Amplitude            | 2.4 V open circuited, 1.2 V into 50 ohms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |